Digital Principles and Computer Organization: Unit III: Computer Fundamentals

Two marks Questions with Answers

Computer Fundamentals - Digital Principles and Computer Organization

Computer architecture is defined as the functional operation of the individual H/W unit in a computer system and the flow of information among the control of those units.

Two Marks Questions

with Answers

6.1 Functional Units of

Digital Computer

Q.1 Define computer architecture.

Ans.:Computer

architecture is defined as the functional operation of the individual H/W unit

in a computer system and the flow of information among the control of those

units.

Q.2 Define computer H/W.

Ans. : Computer H/W is

the electronic circuit and electro mechanical equipment that constitutes the

computer.

Q.3 Name the functional units of a

computer. AU: Dec.-08

Ans. : The functional

units of a computer are:

1. Input unit

2. Output unit

3. Control unit

4. Memory unit

5. Arithmetic and logical unit

Q.4 What is meant by Central Processing

Unit (CPU)? AU: Dec.-09

Ans. : The arithmetic

and logic unit in conjunction with control unit is commonly called Central

Processing Unit (CPU).

Q.5 What is the function of input unit ?

Ans. : A computer

accepts a digitally coded information through input unit using input devices

such as keyboard and mouse.

Q.6 What are the functions of control

unit?

Ans. : The control

unit co-ordinates and controls the activities amongst the functional units. The

basic function of control unit is to fetch the instructions stored in the main

memory, identify the operations and the devices involved in it, and accordingly

generate control signals to execute the desired operations.

Q.7 What is the function of arithmetic

and logic unit ?

Ans. : The Arithmetic

and Logic Unit (ALU) is responsible for performing arithmetic operations such

as add, subtract, division and multiplication, and logical operations such as

ANDing, ORing, Inverting etc.

6.2 Von Neumann Architecture

Q.8 List the features of Von Neumann

architecture.

Ans. :•It uses stored

program concept. The program (instructions) and

data are stored in a single read-write

memory.

• The contents of read-write memory are

addressable by location, without regard to the type of data contained there.

• Execution of instructions occurs in a

sequential manner (unless explicitly modified) from one instruction to the

next.

Q.9 What is Von Neumann bottleneck ?

Ans. : Von Neumann

Bottleneck Because of the stored program architecture of Von-Neumann machine,

the processor performance is tightly bound to the memory performance. That is,

since we need to access memory at least once per cycle to read an instruction,

the processor can only operate as fast as the memory. This is sometimes known

as the Von Neumann bottleneck or memory wall.

Q.10 What is the role of MAR and MDR ?

Ans. : The MAR (memory

address register) is used to hold the address of the location to or from which

data are to be transferred and the MDR(memory data register) contains the data

to be written into or read out of the addressed location.

Q.11 What is the role of IR ?

Ans. : Instruction

Register (IR) contains the instruction being executed. Its output is available

to the control circuits, which generate the timing signals for controlling the

processing circuits needed to execute the instructions.

Q.12 What is the role of PC ?

Ans. :The Program

Counter (PC) register keeps track of the execution of the program. It contains

the memory address of the instruction currently being executed. During the

execution of the current instruction, the contents of the PC are updated to

correspond to the address of the next instructions to be executed.

6.3 Operations of the Computer

Hardware

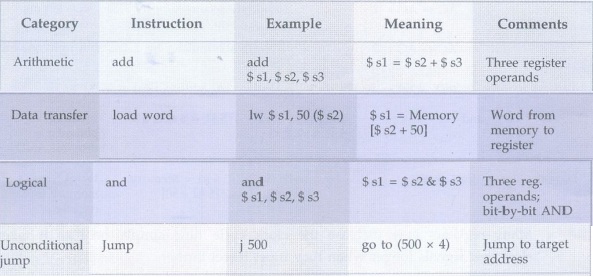

Q.13 Classify the instructions based on

the operations they perform and give one example to each category. AU: Dec.-18

Ans. :Refer section

6.3.1.

• Arithmetic

• Data transfer

• Logical

• Conditional branch

• Unconditional jump.

6.4 Operands of the Computer

Hardware

Q.14 What do you mean by alignment

restriction?

Ans. :

• In MIPS, the registers are 32-bit;

hence, the word size is 32-bit (4 bytes).

• Since most memories are byte (8-bits)

oriented, virtually all architectures today address individual bytes. However,

the byte should be the starting byte of the word.

• Therefore, in MIPS, words must start at

addresses that are multiples of 4. This requirement is called an alignment

restriction and many architectures have it.

Q.15 Why are the most frequently used

variables stored in registers ?

Ans. :Registers take

less time to access and have higher throughput than memory. Hence, the compiler

tries to keep the most frequently used variables in registers.

Q.16 What is spilling registers ?

Ans. :The process of

putting less commonly used variables (or those needed later) into memory is

called spilling registers.

6.5 Instructions

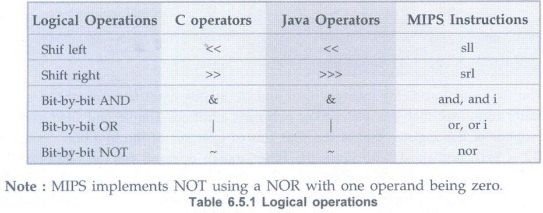

Q.17 List various logical operations

supported by MIPS.

Ans. : Refer section

6.5.1.

Q.18 List the decision making

instructions supported by MIPS assembly language.

Ans. :Refer section

6.5.2.

• MIPS assembly language includes two decision-making instructions, similar to an if statement with a go to.

• beq register1, register2, L1: This instruction means go to the statement labeled L1 if the value in register1 equals the value in register2. The mnemonic beq stands for branch if equal.

• bne register1, register2, L1: It means go to the statement labeled L1 if the value in register1 does not equal the value in register2. The mnemonic bne stands for branch if not equal. These two instructions are called conditional branches.

6.6 Instruction

Set Architecture (ISA)

Q.19 What is Instruction set

architecture ?AU : Dec-15

Ans. : One of the most

imporant abstraction is the interface between the hardware and the lowest-level

softwrae. Because of its importance, it is given a special name:The instruction

set architecture of a computer. It includes anything programmer needs to know

to make a binary machine language program work correctly, including

instructions, I/O devices and so on.

6.7 Memory Locations and

Addresses

Q.20 What do you mean by big endian ?

Ans. : When lower byte

addresses are used for the more significant bytes (the leftmost bytes) of the

word, addressing is called big endian.

Q.21 What do you mean by little endian ?

Ans. : When the lower

byte addresses are used for, the less significant bytes (the rightmost byte) of

the word, addressing is called little-endian.

Q.22 What are aligned addresses ?

Ans. : Word length is

typically a multiple of 8, common CPU word length being 8, 16, 32 and 64-bits.

When word lengths are more than 8-bits, we must take special care while

accessing words. In the case of a 32-bit word length, natural word boundaries

occur at addresses 0, 4, 8, In general, words are said to be aligned in memory

if they begin at the natural word boundaries. The addresses of such words are

called aligned addresses.

6.9

Instruction and Instruction Sequencing

Q.23 What are the various types of

operations required for instructions ?

Ans. :• Data transfers

between the main memory and the CPU registers

•Arithmetic and logic operation on data

• Program sequencing and control

• I/O transfers.

Q.24 What is operation code ?

Ans. :The operation

code field in the instruction specifies the operation to be performed. The

operation is specified by binary code, hence the name operation code or simply

opcode.

Q.25 List various instruction formats

with example.

Ans. :1. Three-address

instruction - add a,b,c

2. Two-address instruction - add a,b

3. One address instruction - add a.

Q.26 What do you mean by zero address

instruction ?

Ans. : It is also

possible to use instruction where the locations of all operand are defined

implicitly. This operand of the use of the method for storing the operand in

which called push down stack. Such instructions are sometimes referred to as

zero address instructions.

6.10 Addressing Modes

Q.27 What are addressing modes ?

Ans. : The different

ways that a processor can access data are referred to as addressing schemes or

addressing modes.

Q.28 List different addressing modes.

Ans. : 1. Register

Mode

2. Absolute Mode or Direct Mode

3. Immediate Mode

4. Indirect Mode

5. Index Mode

6. Relative Mode

7. Autoincrement Mode

8. Autodecrement Mode

Q.29 Differentiate direct and indirect

addressing mode.AU: Dec.-08

Ans. : In direct

addressing mode the address of the location of the operand is given explicitly

as a part of the instruction. On the other hand, in indirect addressing mode,

the effective address of the operand is the contents of a register or the main

memory location whose address is given explicitly in the instruction.

Q.30 State the basic addressing modes

supported by RISC processor.

Ans. :The RISC

processor has three basic addressing modes:

• Register addressing

• Immediate operand and

• Relative to PC addressing for branch

instructions.

Q.31 What is relative addressing mode? When is it used? (Refer section 6.10) AU: June-12

Here, the referenced register is program counter (PC) and hence this addressing mode is also known as PC-relative addressing.

The effective address is determined by adding the contents of PC to the address field. EA = PC + Address part of instruction.

The address part is a signed number so that it is possible to have branch target location either before or after the branch instruction. This addressing mode is commonly used to specify the target address in branch instructions.

• Example: JNZ BACK: This instruction causes program execution to go to the branch target location identified by the name BACK, if the branch condition is satisfied.

Q.32 What are addressing modes ?(Refer

section 6.10)

Part of the programming flexibility for each processor is the number and different kind of ways the programmer can refer to data stored in the memory or I/O device. The different ways that a processor can access data are referred to as addressing schemes or addressing modes.

Q.33 What do you mean by effective

address ?(Refer section 6.10)

• An address computed by the processor when executing a memory access or branch instruction or when fetching the next sequential instruction is known as Effective Address (EA). An effective address can be made up from as many as three elements: The base, index and displacement.

• An addressing mode specifies how to calculate the effective of an operand by using elements of effective information held in registers and/or constants contained within a machine instruction or elsewhere.

Q.34 List any four addressing modes ?(Refer

section 6.10)

1. Register addressing mode.

2. Absolute or direct addressing mode.

3. Immediate addressing mode.

4. Indirect addressing mode.

5. Register indirect addressing mode.

6. Displacement addressing mode.

7. Relative addressing mode.

8. Base register addressing.

9. Index addressing mode.

10. Auto-increment addressing mode.

11. Auto-decrement addressing mode.

12. Stack addressing mode.

Q.35 What is immediate addressing mode ?(Refer

section 6.10)

The operand is given explicitly in the instruction.

• Example :MOV #20, A: This instruction copies operand 20 in the register A. The sign # in front of the value of an operand is used to indicate that this value is an immediate operand.

Q.37 What is displacement addressing mode

?(Refer

section 6.10)

This addressing mode combines the capabilities of direct addressing and register indirect addressing. In this addressing mode, instruction has two address fields: Value and referenced register. The effective address is computed by adding contentsof referenced register to value.

EA =Value + (R).

Three common variation of displacement addressing are :

• Relative addressing

• Base register addressing

• Index addressing.

Q.38 What is base register addressing

mode ?(Refer section 6.10)

In this addressing mode, the referenced register contains the main memory address and address field contains the displacement. Displacement is usually unsigned integer number. EA = (R) + Displacement.

• Example: MOV [R+8], A: This instruction copies the contents of memory whose address is determined by adding the contents of register R and displacement 8 to the register A.

Q.39 What is index addressing mode ?(Refer

section 6.10)

In this addressing mode, the address field references the main memory and the referenced register contains a positive displacement from that address. EA = Memory address + (R).

The indexing is a technique that allows programmer to point or refer the data (operand) stored in sequential memory locations one by one. It is an efficient mechanism for performing iterative operations.

• Example: MOV [R1 + RI], R: In this instruction main memory address is given by register R1 and the referenced register RI gives the positive displacement. The contents of the memory address generated by the addition of main memory address and displacement is copied to register R.

Q.40 What is autoincrement addressing mode ?(Refer section 6.10) AU: May-16

The effective address of the operand is the contents of a register specified in the instruction. After accessing the operand, the contents of this register are incremented to address the next location.

• Example: MOV R0, (R2)+: The above instruction copies the contents of register RO into the memory location whose address is specified by the contents of register R2. After copy operation, the contents of register R2 are automatically incremented by 1.

Q.41 What is autodecrement addressing mode ?(Refer section 6.10) AU: May-16

The contents of a register specified in the instruction are decremented and then they are used as an effective address to access a memory location.

• Example: MOV - (R0), R1: This instruction, initially decrements the contents of register RO and then the decremented contents of register RO are used to address the memory location. Finally, the contents from the addressed memory location are copied into the register R1.

Q.42 What is stack addressing mode ?(Refer

section 6.10)

A stack is linear array of reserved memory locations. It is associated with a pointer called Stack Pointer (SP).

In stack addressing mode, stack pointer always contains the address of Top Of Stack (TOS) where the operand is to be stored or located. Thus, the address of the operand (source or destination) is the contents of stack pointer.

This addressing mode is the special case of register indirect addressing where referenced register is a stack pointer.

Usually, stack grows in the direction of descending addresses, (descending stack), starting from a high address and progressing to lower one. In this stack, SP is decremented before any items are appended (pushed) on stack and SP is incremented after any items popped from the stack.

• Example: PUSH R: This instruction decrements SP and copies the contents of register R on to the top of stack pointed by stack pointer.

Q.43 Brief about relative addressing mode with an example. (Refer section 6.10)

Here, the referenced register is program counter (PC) and hence this addressing mode is also known as PC-relative addressing.

The effective address is determined by adding the contents of PC to the address field. EA = PC + Address part of instruction.

The address part is a signed number so that it is possible to have branch target location either before or after the branch instruction. This addressing mode is commonly used to specify the target address in branch instructions.

• Example: JNZ BACK: This instruction causes program execution to go to the branch target location identified by the name BACK, if the branch condition is satisfied.

Q.44 What is meant by an addressing mode

? Mention most important of them. (Refer section 6.10) AU:

June-11

Part of the programming flexibility for each processor is the number and different kind of ways the programmer can refer to data stored in the memory or I/O device. The different ways that a processor can access data are referred to as addressing schemes or addressing modes.

An addressing mode specifies how to calculate the effective of an operand by using elements of effective information held in registers and/or constants contained within a machine instruction or elsewhere.

Q.45 Distinguish between autoincrement and autodecrement addressing mode. (Refer section 6.10) AU: May-17

Autoincrement addressing mode: The effective address of the operand is the contents of a register specified in the instruction. After accessing the operand, the contents of this register are incremented to address the next location.

• Example: MOV R0, (R2)+: The above instruction copies the contents of register RO into the memory location whose address is specified by the contents of register R2. After copy operation, the contents of register R2 are automatically incremented by 1.

Autodecrement addressing mode: The contents of a register specified in the instruction are decremented and then they are used as an effective address to access a memory location.

• Example: MOV - (R0), R1: This instruction, initially decrements the contents of register RO and then the decremented contents of register RO are used to address the memory location. Finally, the contents from the addressed memory location are copied into the register R1.

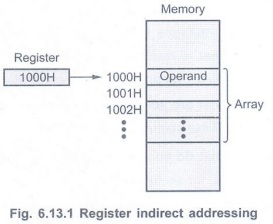

Q.46 State the need for indirect addressing mode. Give an example. AU : May-17

Ans. : In indirect

addressing mode, the instruction specifies the address where the address of the

operand is located. In case of register indirect addressing, the address of the

operand is specified by the contents of the register. These operating modes are

needed when we need to access arrays. Specifically, in register indirect addressing,

registers are used as pointers and they are very useful for dealing with arrays

or tables of simple data values.

Consider Fig. 6.13.1, where a data

structure consists of a sequence of consecutive byte values. The pointer register

contains (1000) H, corresponding to the first item in the structure. To access

item 2 in the structure we only need to increment the value in the pointer

register.

6.12 Interaction between

Assembly and Higher Level Language

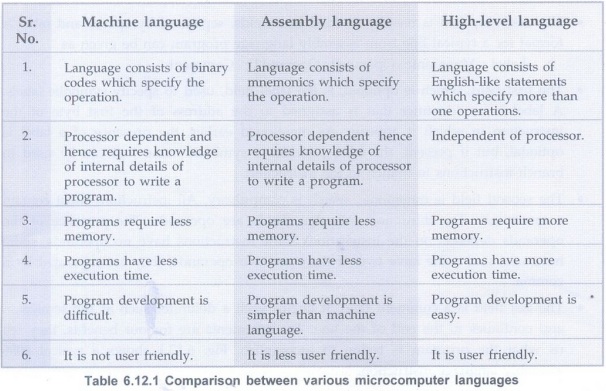

Q.47 Compare machine level, assembly

level and high level languages.

(Refer section 6.12.3)

Q.48 Define compiler.

Ans. :A compiler is a

program which translates the source code written in a high-level language into

computer-readable machine language that can be directly loaded and executed.

Q.49 Define interpreter.

Ans. :An interpreter

translates a high-level language statement in a source program to a machine

code and executes it immediately, before translating the next source language

statement. When an error is found, the execution of the program is halted and

an error message is displayed on the screen of the computer.

Digital Principles and Computer Organization: Unit III: Computer Fundamentals : Tag: : Computer Fundamentals - Digital Principles and Computer Organization - Two marks Questions with Answers

Related Topics

Related Subjects

Digital Principles and Computer Organization

CS3351 3rd Semester CSE Dept | 2021 Regulation | 3rd Semester CSE Dept 2021 Regulation