Digital Principles and Computer Organization: Unit II (a): Synchronous Sequential Logic

Realization of One Flip-Flop using Other Flip-Flop

Synchronous Sequential Logic - Digital Principles and Computer Organization

It is possible to convert one flip-flop into another flip-flop with some additional gates or simply doing some extra connection.

Realization of One

Flip-Flop using Other Flip-Flop

AU: May-03,05,11,14,17,

Dec.-03,04,08,09,10,11,16

• It is possible to convert one flip-flop

into another flip-flop with some additional gates or simply doing some extra

connection.

SR Flip-Flop to D Flip-Flop

• The excitation table for above

conversion is as shown in Table 2.6.1.

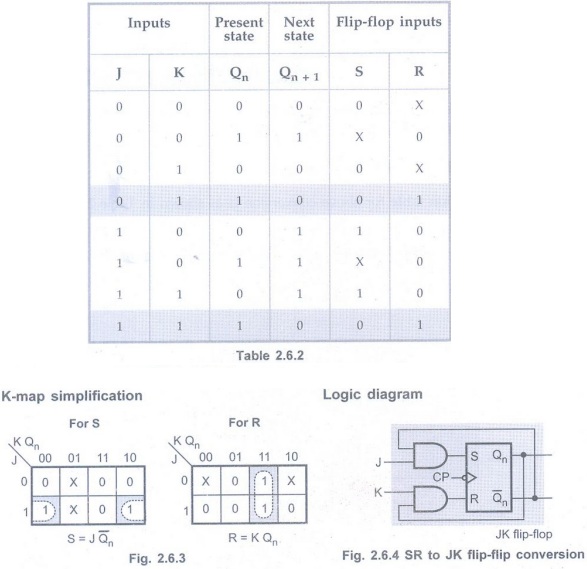

SR Flip-Flop to JK Flip-Flop

• The excitation table for above

conversion is as shown in Table 2.6.2.

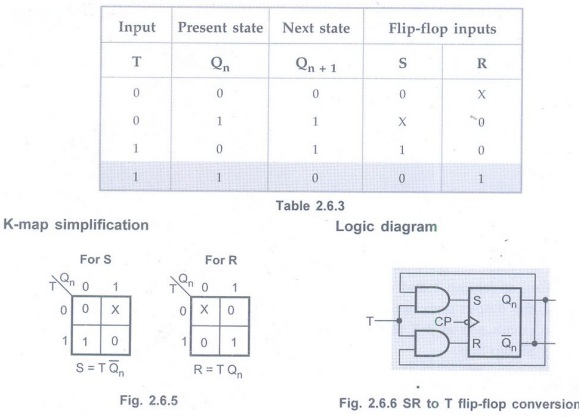

SR Flip-Flop to T Flip-Flop

• The excitation table for above

conversion is as shown in the Table 2.6.3.

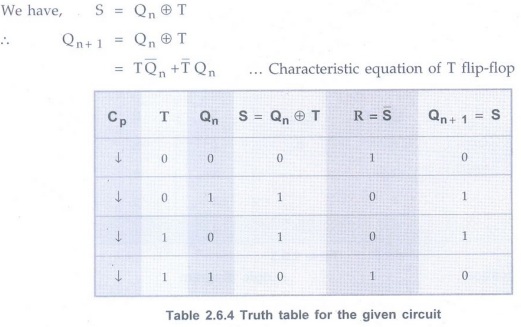

If we apply clock pulses to the circuit, the circuit output will toggle from 0 to 1 and 1 to 0. Thus, we can build 1-bit counter using SR flip-flop by converting it to T flip-flop.

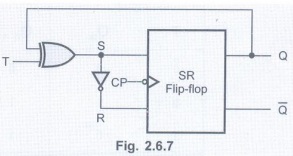

Example 2.6.1

Prepare the truth table for the circuit of Fig. 2.6.7 and show that it acts as a

T-type flip-flop.

Solution:

For SR flip-flop,

Qn+1 = S + Ȓ Qn …Characteristics

equation R = Ŝ

= S + S Qn

= S(1 + Qn) = S

• Looking at column 1 and column 5 of the

Table 2.6.4 we can conclude that when T=0, the output does not change and when

T = 1, the output toggles. Thus, the given circuit acts as a T flip-flop. This

is another way of implementing T flip-flop using SR flip-flop.

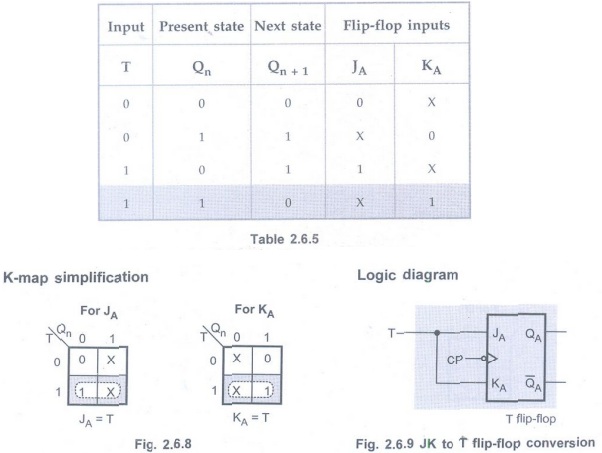

JK Flip-Flop to T Flip-Flop

• The excitation table for above

conversion is as shown in Table 2.6.5.

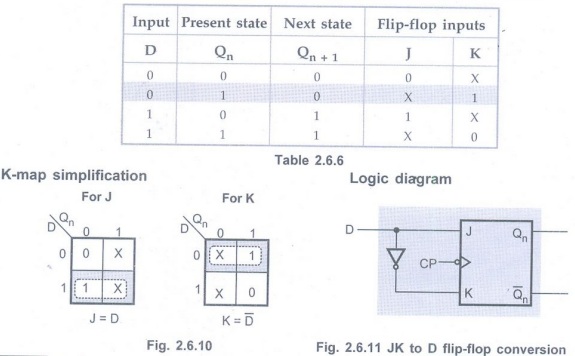

JK Flip-Flop to D Flip-Flop

• The excitation table for above

conversion is as shown in the Table 2.6.6.

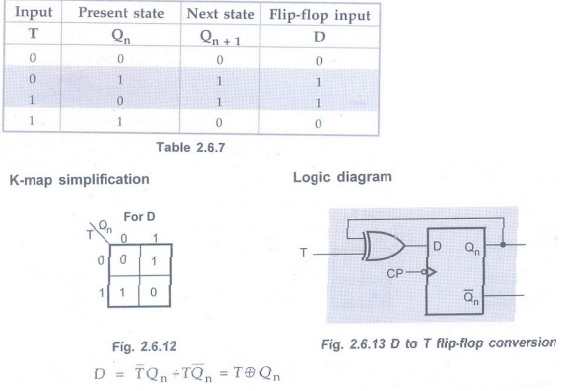

D Flip-Flop to T Flip-Flop

The excitation table for above

conversion is as shown in the Table 2.6.7.

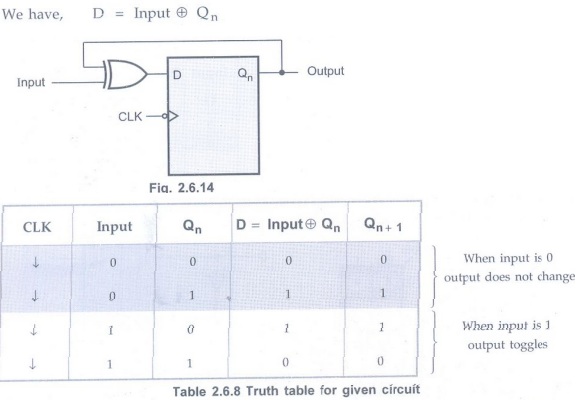

Example 2.6.2

Analyze the circuit and prove that it is equivalent to T flip-flop.

Solution : To analyze the circuit means to derive the truth table for it.

• In the above circuit, output does not

change when input is 0 and it toggles when input is 1. This is the

characteristics of T flip-flop. Hence, the given circuit is T flip-flop

constructed using D flip-flop.

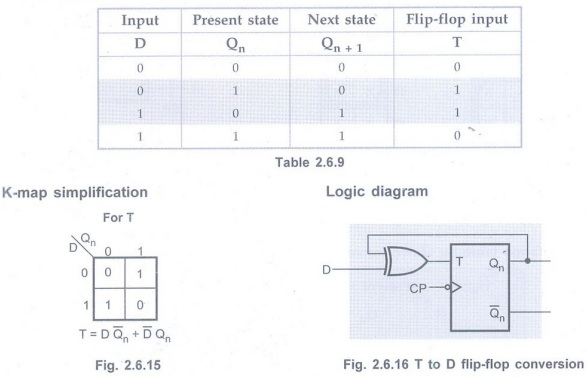

T Flip-Flop to D Flip-Flop

The excitation table for above

conversion is as shown in the Table 2.6.9.

JK Flip-Flop to SR Flip-Flop

The excitation table for above

conversion is as shown in Table 2.6.10.

D Flip-Flop to SR Flip-Flop

The excitation table for above

conversion is as shown in the Table 2.6.11.

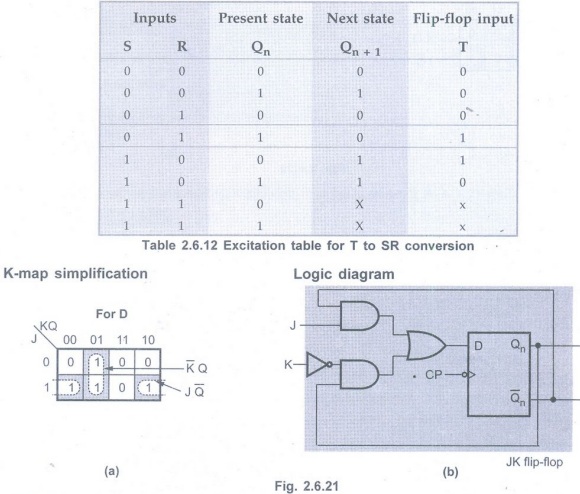

T Flip-Flop to SR Flip-Flop

The excitation table for conversion of T

FF into an SR FF is as shown in the Table 2.6.12.

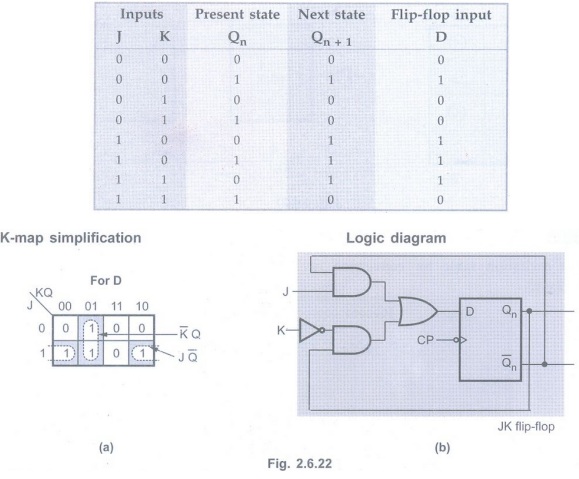

D Flip-Flop to JK Flip-Flop

The excitation table for conversion of D

flip-flop to JK flip-flop.

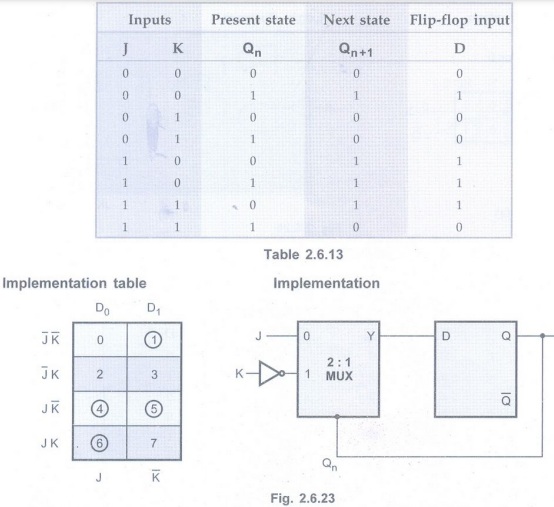

Example 2.6.3

Construct a JK flip-flop using a D flip-flop, a 2 x 1 multiplexer and an

inverter.AU: Dec.-08, Marks 4

Solution:

The excitation table for above conversion is as shown in the Table 2.6.13.

Review Questions

1. Convert JK flip-flop to D flip-flop. AU:

May-03, 05, Dec.-03, Marks 2

2. Convert D flip-flop into T flip-flop. AU:

Dec.-03, May-11,14, Marks 6

3. Convert JK flip-flop to T flip-flop. AU:

Dec.-04, 10, Marks 2

4. Convert a SR flip-flop into a D

flip-flop. AU: Dec.-08, Marks 8

5. Convert a T-FF into an S-R FF. Draw

the circuit. AU: Dec.-08, Marks 2

6. How will you convert a D flip-flop into JK flip-flop? AU: Dec.-09, 11, May-14, Marks 8

7. Convert SR flip-flop into JK

flip-flop.

8. Convert SR flip-flop into T

flip-flop.

9. Implement T-flip flop and JK flip flop using D flip flop. AU: Dec.-16, May-17, Marks 16

10. Implement JK flip flop using D flip

flop. AU: Dec.-16, Marks 8

Digital Principles and Computer Organization: Unit II (a): Synchronous Sequential Logic : Tag: : Synchronous Sequential Logic - Digital Principles and Computer Organization - Realization of One Flip-Flop using Other Flip-Flop

Related Topics

Related Subjects

Digital Principles and Computer Organization

CS3351 3rd Semester CSE Dept | 2021 Regulation | 3rd Semester CSE Dept 2021 Regulation