Digital Principles and Computer Organization: Unit III: Computer Fundamentals

Operands of the Computer Hardware

Computer Fundamentals - Digital Principles and Computer Organization

In MIPS, the operands of arithmetic instructions are restricted; they must be from a limited number of special locations built directly in hardware called registers.

Operands of the Computer Hardware

AU: Dec.-18

Register Operands

• In MIPS, the operands of arithmetic

instructions are restricted; they must be from a limited number of special

locations built directly in hardware called registers.

• Registers are primitives used in

hardware design that are also visible to the programmer.

• The size of a register in the MIPS

architecture is 32-bits; groups of 32-bits occur so frequently that they are

given the name word in the MIPS architecture.

• MIP computers have a limited number of

registers, typically 32. This is one of the significant differences between the

variables of a programming language and registers.

• MIPS limits the number of 32-bit

registers to 32. The reason for the limit of 32 registers are:

• Many registers may increase the clock

cycle time simply because it takes electronic signals longer when they must

travel farther.

• More registers more bits in the

instruction format.

Memory Operands

• The processor can keep only a small

amount of data in registers, but computer memory contains billions of data

elements. Hence, more data and data structures such as arrays and structures

are kept in the computer memory.

• Memory is just a large,

single-dimensional array, with the address as the index to that array, starting

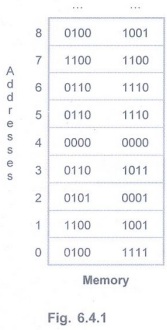

at 0. This is illustrated in Fig. 6.4.1

• As mentioned above, arithmetic

operations occur only on registers in MIPS instructions; thus, MIPS must

include instructions that transfer data between memory and registers. Such

instructions are called data transfer instructions.

• The instruction must have the memory

address to access a word in the memory. For example, in Fig. 6.4.1, the address

of the fourth data element is 3, and the value of Memory [3] is 0110 1011.

Load Instruction

• The data transfer instruction that

copies data from memory to a register is called load.

• The format of the load instruction is

divided into three parts:

• Name of the operation followed by

• the register to be loaded, then

• a constant and register used to access

memory.

• The sum of the constant portion of the

instruction and the contents of the second register forms the memory address.

• In MIPS, name for this instruction is

lw, which stands for load word.

Example 6.4.1

Let's assume that A is an array of 50 words and that the compiler has

associated the variables p and q with the registers $s1 and $s2. Let's also

assume that the array's starting address, or base address, is in $s3. Compile

this C assignment statement : p = q + A[7];

Solution:

Here, one of the operands is in the memory, so we have first to transfer A[7]

to a temporary register. This is achieved by -

lw $t0, 7 ($s3)// Temporary reg $t0 gets

A[7]

The address of this array element is the

sum of the base of the array A, found in register $s3, plus the number to

select element 7.

The instruction must add q (contained in

$s2) to A[7] (contained in $t0) and put the sum in the register corresponding

to p (associated with $s1). This is achieved by -

add $s1, $s2, $to// p = q + A[7]

Note:

The constant in a data transfer instruction is called the offset, and the

register added to form the address ($s3) is called the base register.

Alignment Restriction

• In MIPS, the registers are 32-bit;

hence, the word size is 32-bit (4 bytes).

• Since most memories are byte (8-bits)

oriented, virtually all architectures today address individual bytes. However,

the byte should be the starting byte of the word.

• Therefore, in MIPS, words must start

at addresses that are multiples of 4. This requirement is called an alignment

restriction and many architectures have it.

• The 32-bit word size also affects the

array index of the memory. To get the proper byte address, the offset to be

added to the base register $s3 must be multiplied by 4. For example, to access

a byte from A[5], the offset to be added to the base register, $s3 must be 5 x

4 or 20.

Store Instruction

• The instruction complementary to load

is called store; it copies data from a register to memory.

• The format of a store is similar to

that of a load :

• Name of the operation, followed by

• the register to be stored, then offset

to select the array element and finally

• the base register.

• Once again, in MIPS, the address of the

operand is specified in two parts: Offset and base.

• In MIPS name for this instruction is

sw, which stands for store word.

Example 6.4.2

Assume variable p is associated with register $s2 and the base address of the array

A is in $s3. What is the MIPS assembly code for the C assignment statement

A[10] = p + A[7]?

Solution:

We have first to transfer A[7] to a temporary register. This is achieved by lw

$t0, 28 ($s3) // Temporary reg $t0 gets A[7]

The instruction must add p (contained in

$s2) to A[7] (contained in $t0) and put the sum in the temporary register since

it is finally should be stored in memory.

Add $t0,$s2,$t0 //Temporary reg $t0 gets p + A[7]

The final destination stores the sum

into A[10], using 40 (4 × 10) as the offset and register $s3 as the base

register.

sw $t0, 40 ($s3)// Stores p + A[7] back

into A[10]

Register Vs Memory

• A MIPS data transfer instruction only

reads one operand or writes one operand, without operating on it. However, MIPS

arithmetic instruction can read two registers, operate on them and write the

result.

• Thus, registers take less time to

access and have higher throughput than memory. •Many programs have more

variables than computers have registers. Consequently, the compiler tries to

keep the most frequently used variables in registers and places the rest in

memory, using loads and stores to move variables between registers and memory.

• The process of putting less commonly

used variables (or those needed later) into memory is called spilling

registers.

Constant or Immediate Operands

• The arithmetic instructions in which

one operand may be a constant. This constant operand is also known as an

immediate operand. For example,

addi $s2, $s2, 5 // $s2 = $s2 + 5

• The above instruction is an add

immediate instruction (addi), and it adds 5 in the contents of register $s2.

• By including constants inside

arithmetic instructions, operations are much faster and use less energy than if

constants were loaded from memory.

Example 6.4.3

Assume variable b is associated with register $s2 and the base address of the

array A is in $s3. What is the MIPS assembly code for the C assignment

statement below? A[10] = A[5] + b;

Solution:

Although there is a single operation in the C statement, now two of the

operands are in memory, so we need even more MIPS instructions.

lw $t0,20($s3)//Temporary reg $t0 gets

A[5] using 16 (4 X 5)

add $t0,$s2,$t0// Temporary reg $t0 gets

A[5] + b

sw $t0,40($s3)// Stores b + A[5] back

into A[10] using 40 (4 x10) as the offset

and register$s3 as the base

register.

Example 6.4.4

Assume that the variables f, g, h, i, and j are assigned to registers $s0, $s1,

$s2, $s3, and $s4, respectively. Assume that the base address of the arrays A

and B are in registers $s6 and $s7, respectively. C Code: f = 8 + A[B[4]-B[3]];

For the C statement above, what is the corresponding MIPS assembly code?

Solution:

lw $t0, 16($s7)// $to = B[4]

lw $t1, 12($s7)// $t1 = B[3]

sub $to, $to, $t1// $to = B[4] - B[3]

sll $to, $t0, 2// $to =$to * 4

add $to, $to, $s6// $to =&A[B[4] -

B[3]]

lw $t1, 0($t0)// $t1=A[B[4] - B[3]]

add $s0, $s1, $t1// f g + A[B[4] - B[3]

Example 6.4.5

Assume that the variables ƒ and g are assigned to registers $50 and $s1

respectively. Assume that the base address of the array A is in register $s2.

Assume f is zero initially.

f = -8 - A[4]

A[5] = ƒ + 100;

Translate the above C statements into

MIPS code. How many MIPS assembly instructions are needed to perform the C

statements and how many different registers are needed to carry out the C

statements ? AU: Dec.-18, Marks 5

Solution:

lw $t0, 16[$s2]// Save A[4] into

register to

sub $s0, $s0, $t0// f = f - A[4]

sub $s0, $s0, $s1//f=f-g

add i $s0, $s0, 100// f + 100

lw 20[$s2], $s0// Save f into A[5]

For registers are needed to carry out

the C statements

Example 6.4.6

The following problems deal with translating from C to MIPS. Assume that the

variables f, g, h, i, and j are assigned to registers $50, $s1, $s2, $s3, and

$s4, respectively. Assume that the base address of the arrays A and B are in

registers $s6 and $s7, respectively.

a. f = - g - A[5];

b. B[7] = A[i – j];

Solution :

a.

lw $t0, 20[$s6]// save A[5] into

register to

add $to, $to, $s1// g + A[5]

sub $s0, $zero, $to// f=0-( g + A[5])

b.

sub $to, $s3, $s4 //i -j

add $to, $to, $s6// puts i - j into

array

lw $t0, 0($t0) // makes to its own

address

sw $t0, 28($s7)// throws B[7] into

register t0

Review Questions

1. Write a note on the operands of the

computer hardware.

2. Explain the load instruction.

3. Explain the store instruction.

4. What do you mean by alignment

restriction?

5. What do you mean by spilling

registers ?

6. Why are frequently used variables

stored in registers ?

Digital Principles and Computer Organization: Unit III: Computer Fundamentals : Tag: : Computer Fundamentals - Digital Principles and Computer Organization - Operands of the Computer Hardware

Related Topics

Related Subjects

Digital Principles and Computer Organization

CS3351 3rd Semester CSE Dept | 2021 Regulation | 3rd Semester CSE Dept 2021 Regulation