Digital Principles and Computer Organization: Unit I: Combinational Logic

Multiplexers

Combinational Logic - Digital Principles and Computer Organization

In digital systems, many times it is necessary to select single data line from several data-input lines, and the data from the selected data line should be available on the output. The digital circuit which does this task is a multiplexer.

Multiplexers

AU:

Dec.-08,11,14, 16,19, May-04,06,07,11,12,14,17

In digital systems, many times it is

necessary to select single data line from several data-input lines, and the

data from the selected data line should be available on the output. The digital

circuit which does this task is a multiplexer.

It is a digital switch. It allows

digital information from several sources to be routed onto a single output

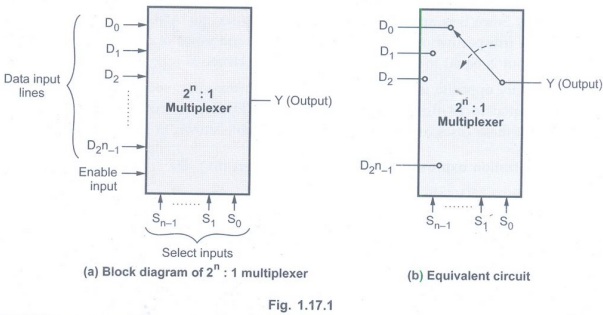

line, as shown in the Fig. 1.17.1. The basic multiplexer has several data-input

lines and a single output line. The selection of a particular input line is

controlled by a set of selection lines. Since multiplexer selects one of the

input and routes it to output, it is also known as data selector. Normally,

there are

2 : 1 Multiplexer

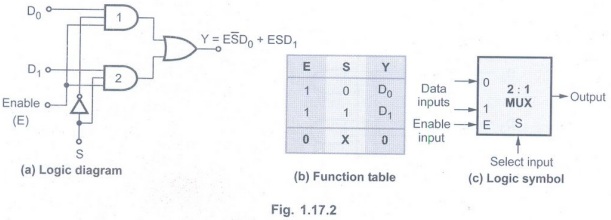

• Fig. 1.17.2 (a) shows 2: 1

multiplexer.

• D0 to is applied as an

input to one AND gate and D1 is applied as an input to another AND

gate.

• Enable input is applied to both gates

as one input.

• Selection line S is connected as second input to second AND gate.,

• An inverted S is applied as second

input to first AND gate.

• Outputs of both AND gates are applied

as inputs to OR gate.

Working

• When E = 0, output is 0, i.e. Y = 0

irrespective of any input condition.

• When E = 1, the circuit works as

follows:

a. When S = 0, the inverted S, that is 1

gets applied as second input to first AND gate. Since S is applied directly as

input to second AND gate; its output goes zero irrespective of first input.

Since the second input of first AND gate is 1, its output is equal to its first

input, that is D0. Hence Y = D0.

b. Exactly opposite is the case when S =

1. In this case, second AND gate output is equal to its first input D0

and first AND gate output is 0. Hence Y = D0. Both these cases are

summarized in truth table shown in Fig. 1.17.2 (b).

Deriving realization expression

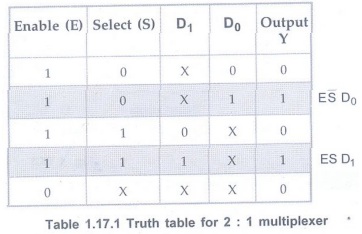

The Table 1.17.1 shows the truth table for 2 : 1 multiplexer. From the truth table it is clear that Y=1 when EŜD0=1 or ESD1=1 as indicated by shaded rows.

4 :1 Multiplexer

• Fig. 1.17. (a) shows 4-to-1 line

multiplexer.

• Each of the four lines, D0 to

D3, is applied to one input of an AND gate.

• Selection lines are decoded to select

a particular AND gate.

• For example, when S1 S0

= 0 1, the AND gate associated with data input D1 has two of

its inputs equal to 1 and the third input connected to D1. The other

three AND gates have at least one input equal to 0, which makes their outputs

equal to 0. The OR gate output is now equal to the value of D1, thus

we can say data bit D1 is routed to the output when S1 S0

= 0 1.

8: 1 Multiplexer

• Fig. 1.17.4 shows 8 : 1 multiplexer.

• There are eight input lines one output

line and three select lines.

• As shown in the function table, the

selection of a particular input line is controlled by three selection lines.

Quadruple 2 to 1 Multiplexer

• In some cases, two or more

multiplexers are enclosed within one IC package, as shown in Fig. 1.17.5.

• The Fig. 1.17.5 shows quadruple 2-to-1

line multiplexer, i.e. four multiplexers, each capable of selecting one of two

input lines.

• Output Y1 can be selected

to be equal to either A2 or B2.

• Output Y2 may have the value

of A2 or B2, and soon.

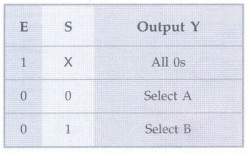

•The selection line S selects one of two

lines in all four multiplexers. The control input E enables the multiplexers in

the 0 state and disables them in the 1 state.

• When E = 1, outputs have all 0's,

regardless of the value of S.

Function Table

Illustrative Examples

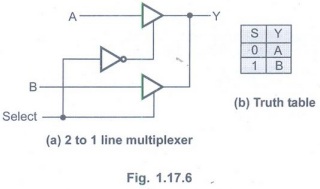

Example 1.17.1 Construct

and explain the working of 2 to 1 line multiplexer using

three-state gates.

Solution :

Three state/tri-state gates exibit three states. Two states: Logic 1 and Logic

0 as in a conventional gate. The third state is a high-impedance state in which

logic behaves like an open circuit. Fig. 1.17.6 (a) shows 2 to 1 line

multiplexer using 2 three-state buffers and an inverter. Since buffers are

tri-state buffer their outputs can be connected together to form a single

output line. The circuit behaves as per the truth table shown in Fig. 1.17.6

(b).

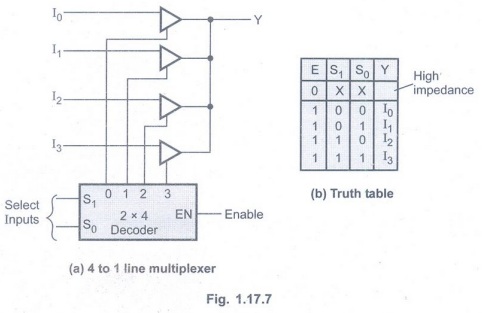

Example 1.17.2

Construct 4 to 1 line multiplexer using three-state gates and decoder.

Solution:

Here, the output of 4 three-state buffers are connected together to form a

single output line. The control inputs for the four buffer are determined using

2: 4 decoder as shown in the Fig. 1.17.7. When S1 S0 =

00, the upper control buffer is selected and I0 signal is routed to

the output. Similarly, according to the select inputs of the decoder one of

input is routed to the output.

Expanding Multiplexers

•It is possible to expand range of

inputs for multiplexer beyond the available range by interconnecting several

multiplexers in cascade.

• The circuit with two or more

multiplexers connected to obtain the multiplexer with more number of inputs is

known as multiplexer tree.

Examples for Understanding

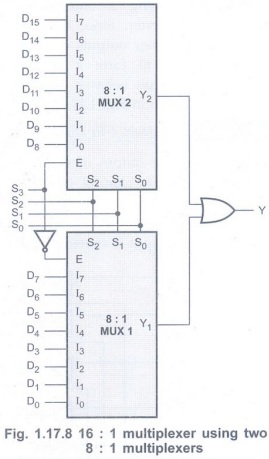

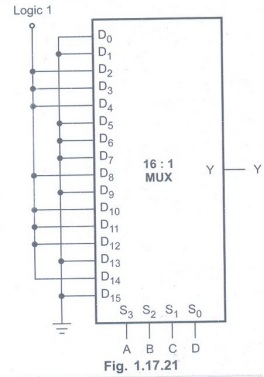

Example 1.17.3 Design

16: 1 multiplexer using 8: 1 multiplexer.

Solution:

Step 1: Connect

the select lines (S2, S1 and S0) of two

multiplexers in parallel.

Step 2: Connect

most significant select line (S3) such that when S3 = 0

MUX 1 is enabled and when S3 = 1, MUX 2 is enabled.

Step 3: Logically

OR the outputs of two multiplexers to obtain the final output Y.

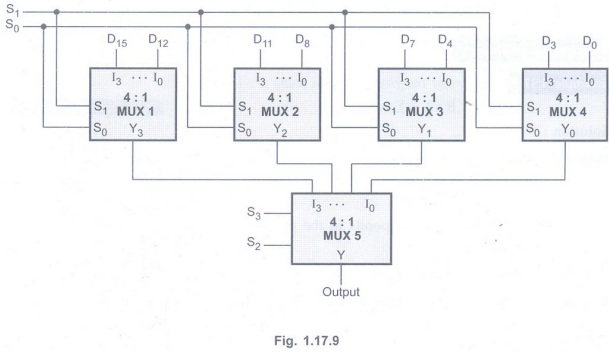

Example 1.17.4 Design 16 : 1 multiplexer using 4 : 1 multiplexers.

Solution : Since there are 16-inputs for the multiplexers we require

four 4 : 1 multiplexers to satisfy input needs. The four outputs of 4 : 1

multiplexers are again multiplexed by 4 : 1 multiplexer to generate final

output.

Step 1 : Connect the select lines (S1 and S0) of

four multiplexers in parallel.

Step 2 : Connect the most significant select lines (S3 and

S2) to the MUX 5.

Step 3 : Connect

the outputs Y0 ,Y1 ,Y2 and Y4 of

four multiplexers as data inputs for the MUX 5, as shown in the Fig. 1.17.9.

Examples for Practice

Example 1.17.5

Design 32: 1 MUX using 8: 1 MUX.

Example 1.17.6

Show how two 2: 1 multiplexers(with no added gates) could be connected to form

a 3: 1 multiplexer. Input selection should be as follows:

If AB = 00, Select I0.

AB = 01, Select I1.

AB = 1 × (B is don't care), Select I2.

Implementation of Combinational Logic using MUX

• A multiplexer consists of a set of AND

gates whose outputs are connected to single OR gate. Because of this

construction any Boolean function in a SOP form can be easily realized using

multiplexer.

• Each AND gate in the multiplexer

represents a minterm.

• In 8 to 1 multiplexer, there are 3

select inputs and 23 minterms.

• By connecting the function variables

directly to the select inputs, a multiplexer can be made to select the AND gate

that corresponds to the minterm in the function.

• If a minterm exists in a function, we

have to connect the AND gate data input to logic 1; otherwise we have to

connect it to logic 0.

Illustrative Examples

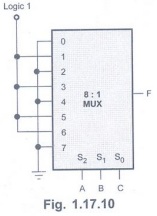

Example 1.17.7

Implement the given function using 8 : 1 multiplexer.

F(A,B,C) = ∑m(1, 3, 5, 6). AU:

Dec.-14, Marks 2

Solution :

Step 1:

Select the multiplexer. Here, Boolean expression has 3 variables, thus we

require 23 = 8:1 multiplexer.

Step 2: Connect

inputs corresponds to the present minterms to logic 1.

Step 3: Connect

remaining inputs to logic 0.

Step 4: Connect

input variables to select lines of MUX.

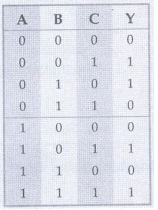

Example 1.17.8

Implement the Boolean function represented by the given truth table using

multiplexer.

Solution :

Step 1: Select

the multiplexer. Here, there are three input variables, thus we require 23

= 8: 1 multiplexer.

Step 2:

Find the minterm expression.

Minterm expression for given truth table

is ∑m (1, 2, 5, 7).

Step 3: Connect

inputs corresponds to the present minterms to logic 1.

Step 4: Connect

remaining inputs to logic 0.

Step 5: Connect

input variables to select lines of MUX.

• In the above example, we have seen the

method for implementing Boolean function of 3 variables with 23 (8)

- to - 1 multiplexer. Similarly, we can implement any Boolean function of

nvariables with 2n - to - 1 multiplexer. However, it is possible to

do better than this.

• If we have Boolean function of n + 1

variables, we take n of these variables and connect them to the selection lines

of a multiplexer. The remaining single variable of the function is used for the

inputs of the multiplexer. In this way we can implement any Boolean function of

n variables with 2n-1- to - 1 multiplexer.

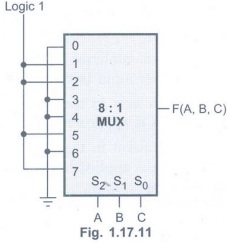

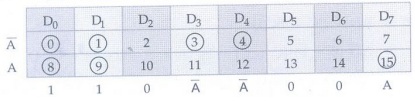

Example 1.17.9 Implement

the following Boolean function using 4: 1 multiplexer. F (A, B, C) = ∑m (1, 3,

5, 6)

Solution :

Step 1: Connect

least significant variables as a select inputs of multiplexer. Here, connect C

to S0 and B to S1.

Step 2: Derive

inputs for multiplexer using implementation table.

As shown in the Fig. 1.17.12 (a) the

implementation table is nothing but the list of the inputs of the multiplexer

and under them list of all the minterms in two rows. The first row lists all

those minterms where A is complemented, and the second row lists all the

minterms with A uncomplemented. The minterms given in the function are circled

and then each column is inspected separately as follows:

•If the two minterms in a column are not

circled, 0 is applied to the corresponding multiplexer input (see column 0).

• If the two minterms in a column are

circled, 1 is applied to the corresponding multiplexer input (see column 1).

• If the minterm in the second row is

circled and minterm in the first row is not circled, A is applied to the

corresponding multiplexer input (see column 2).

• If the minterm in the first row is

circled and minterm in the second row is not circled, Ā is applied to the corresponding

multiplexer input (see column 3).

Step 2:

Implement it using implementation table.

From the Boolean function in the minterm

form can be implemented using 8:1 multiplexer as follows:

Example 1.17.11

Implement the following Boolean function with 8: 1 multiplexer F (A, B, C, D) =

л M (0, 3, 5, 6, 8, 9, 10, 12, 14)

Solution:

Here, instead of minterms, maxterms are specified. Thus, we have to circle

maxterms which are not included in the Boolean function. Fig. 1.17.14 shows the

implementation of Boolean function with 8 : 1 multiplexer.

Example 1.17.12

Implement the following Boolean function with 8: 1 multiplexer. F(A, B, C, D) =

Σ m(0, 2, 6, 10, 11, 12, 13) + d (3, 8, 14)

Solution:

In the given Boolean function three don't care conditions are also specified.

We know that don't care conditions can be treated as either 0s or 1s. Fig.

1.17.15 shows the implementation of given Boolean function using 8:1

multiplexer.

In this example, by taking don't care conditions 8 and 14 as 1s we have eliminated Ā term and hence the inverter.

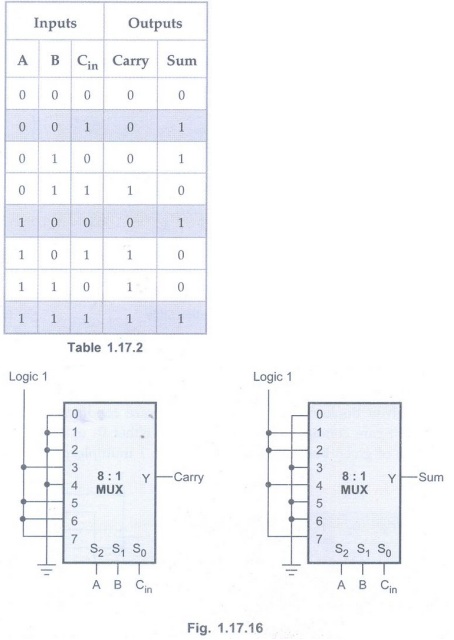

Example 1.17.13 Implement full adder circuit using 8: 1 multiplexer. AU: May-11, Marks 5

Solution :

Example 1.17.14 Implement full adder circuit using dual 4 to 1 multiplexer. AU: May-12, Dec.-14, Marks 8

Solution: Implementation tables :

Example 1.17.15 Realize

F(w, x, y, z) = Σ (1, 4, 6, 7, 8, 9, 10, 11, 15) using 4 to 1 MUX. AU May-04,

Marks 8

Solution :

Example 1.17.16 Design

even parity generator circuit for 4 bit input using multiplexer. AU: May-07

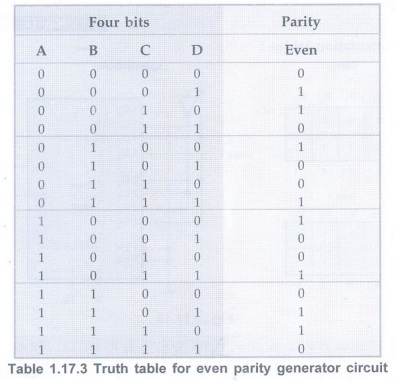

Solution : The

Table 1.17.3 shows the truth table for even parity generator circuit.

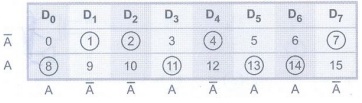

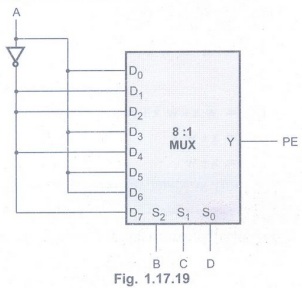

Implementation Table :

Implementation using 8 : 1 multiplexer

Example 1.17.17 A 8 x 1 multiplexer has inputs A, B, and C connected to the selection inputs S2, S1 and S0 respectively. The data inputs I0 to I7 are as follows I0 = I2 = I7 = 0; I3 = I5 = 1; I0 = I4 = D and I6= D'. Determine the Boolean function that the multiplexer implements. AU: Dec.-08, Marks 10.

Solution:

Since input A is the MSB, The D input is LSB. Let us determine the

implementation table for multiplexer from given information.

If I is connected to 0 don't encircle any term. If I is connected to 1, encircle both the terms in a row. If I is connected to Ď, encircle the corresponding term in the column Ď. If I is connected to D, encircle the corresponding term in the column D. This is illustrated in the implementation table of Fig. 1.17.20. Now write down the encircled terms to get the boolean function. It is given as,

F(A, B, C, D) = ∑m (1, 6, 7, 9, 10, 11,

12)

Example 1.17.18

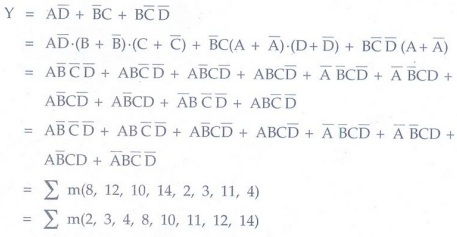

Design a combinational logic using a suitable multiplexer to realize

the following Boolean expression.

Y = ADʹ + B'C + BC' D'. AU May-11,

Marks 10

Solution:

Step 1:

Convert the given Boolean expression in standard form

Step 2:

Implementation

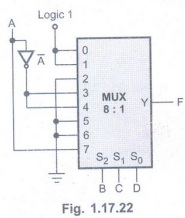

Example 1.17.19

Implement the function with a multiplexer.

F(A, B, C, D) = ∑ (0, 1, 3, 4, 8, 9, 15) AU:

Dec.-08, 11, Marks 6

Solution: Implementation table :

Implementation

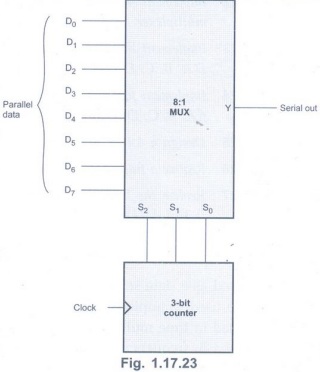

Example 1.17.20 How

can a multiplexer be used to convert 8-bit parallel data into serial form? Draw

the circuit and briefly explain. AU May-06, Marks 2

Solution:

Multiplexer can be used to convert 8-bit parallel data into serial form as

shown in the Fig. 1.17.23.

Here, binary counter is used to drive

the select inputs of the multiplexer so that as binary counter increments its

count, the next bit is available at the output of the multiplexer. The binary

counter counts from 000 to 111, therefore, D0 through D7,

bits are available at the output of multiplexer as serial output.

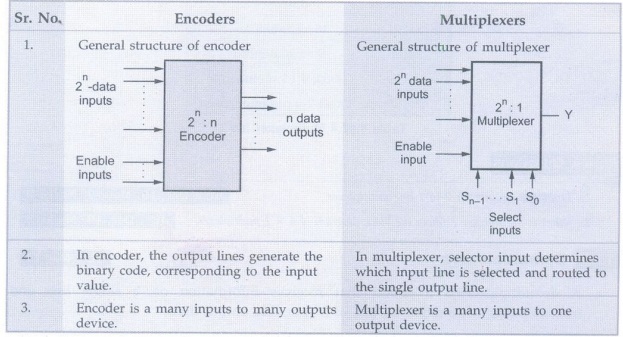

Example 1.17.21 Compare and contrast between encoders and multiplexers. AU May-11, Marks 6

Solution :

Examples for Practice

Example 1.17.22

Implement F (A, B, C, D) =∑ m (0, 1, 3, 4, 8, 9, 15) using 8: 1

multiplexer.

Example 1.17.23

Implement the following Boolean function with 8: 1 mux. F(A, B, C, D) = πM (0,

3, 5, 8, 9, 10, 12, 14).

Example 1.17.24

Implement following function using 16: 1 multiplexer. f(A, B, C, D) = ∑m (1, 9,

10, 14, 18).

Example 1.17.25 Design

a 4 to 1 MUX using a 2 to 4 decoder and basic gates.

Example 1.17.26 Realize

a full adder using 4 x 1 multiplexers.

Example 1.17.27 Realize

the function f(A, B, C, D) = π(1,4,6,10,14). d (0,8,11,15) using i) 16:1 MUX

ii) 8:1 MUX.

Applications of Multiplexer

1. They are used as a data selector to

select one out of many data inputs.

2. They can be used to implement

combinational logic circuit.

3. They are used in time multiplexing

systems.

4. They are used in frequency

multiplexing systems.

5. They are used in A/D and D/A

converter.

6. They are used in data acquisition

systems.

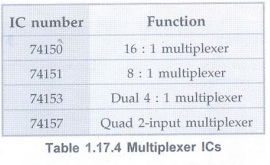

Multiplexer ICs

Review Questions

1. Draw the circuits for 2-to-1 line

multiplexer. AU: Dec.-16, May-17, Marks 2

2. What is multiplexer ? Show the block diagram of 4 x 1 multiplexer. AU: Dec.-19, Marks 2

Digital Principles and Computer Organization: Unit I: Combinational Logic : Tag: : Combinational Logic - Digital Principles and Computer Organization - Multiplexers

Related Topics

Related Subjects

Digital Principles and Computer Organization

CS3351 3rd Semester CSE Dept | 2021 Regulation | 3rd Semester CSE Dept 2021 Regulation