Digital Principles and Computer Organization: Unit V: Memory and I/O

Interrupt I/O

Memory and I/O - Digital Principles and Computer Organization

Sometimes it is necessary to have the computer automatically execute one of a collection of special routines whenever certain conditions exists within a program or the computer system e.g.

Interrupt I/O

AU: Dec.-06, 07, 08, 09, 10, 11, 12, 16,

18, May-06, 07, 08, 09, 12, 13

• Sometimes it is necessary to have the

computer automatically execute one of a collection of special routines whenever

certain conditions exists within a program or the computer system e.g. It is

necessary that computer system should give response to devices such as

keyboard, sensor and other components when they request for service.

• This method provides an external

asynchronous input that would inform the processor that it should complete

whatever instruction that is currently being executed and fetch a new routine

(Interrupt Service Routine) that will service the requesting device. Once this

servicing is completed, the processor would resume exactly where it left off.

The event that causes the interruption is called interrupt and the special

routine executed to service the interrupt is called Interrupt Service Routine

(ISR).

• The interrupt service routine is

different from subroutine because the address of ISR is predefined or it is

available in Interrupt Vector Table (IVT), whereas subroutine address is

necessarily to be given in subroutine CALL instruction. IRET instruction is

used to return from the ISR whereas RET instruction is used to return from

subroutine. IRET instruction restores flag contents along with CS and IP in the

IA-32 architecture; however RET instruction only restores CS and IP contents.

• An interrupt caused by an external

signal is referred as a hardware interrupt.

• Conditional interrupts or interrupts

caused by special instructions are called software interrupts.

Enabling and disabling interrupts

• Most of the processors provide the

masking facility. In the processor those interrupts which can be masked under

software control are called maskable interrupts.

• The interrupts which can not be masked

under software control are called non-maskable interrupts.

• Maskable interrupts are enabled and

disabled under program control. By setting or resetting particular flip-flops

in the processor, interrupts can be masked or unmasked, respectively.

• When masked, processor does not respond

to the interrupt even though the interrupt is activated.

Vectored interrupts

• When the external device interrupts the

processor (interrupt request), processor has to execute interrupt service

routine for servicing that interrupt. If the internal control circuit of the

processor produces a CALL to a predetermined memory location which is the

starting address of interrupt service routine, then that address is called

vector address and such interrupts are called vector interrupts. For vector

interrupts fastest and most flexible response is obtained since such an

interrupt causes a direct hardware-implemented transition to the correct

interrupt-handling program. This technique is called vectoring. When processor

is interrupted, it reads the vector address and loads it into the PC.

Interrupt nesting

• For some devices, a long delay in

responding to an interrupt request may cause error in the operation of

computer. Such interrupts are acknowledged and serviced even though processor is

executing an interrupt service routine for another device. •A system of

interrupts that allows an interrupt service routine to be interrupted is known

as nested interrupts.

Interrupt priority

• When interrupt requests arrive from

two or more devices simultaneously, the processor has to decide which request

should be serviced first and which one should be delayed. The processor takes

the decision with the help of interrupt priorities.

• It accepts the request having the

highest priority.

Recognition of Interrupt and Response to Interrupt

• The CPU recognizes the interrupt when

the external asynchronous input (interrupt input) is asserted (a signal is sent

to the interrupt input) by an I/O device.

• In response to an interrupt a special

sequence of actions are performed. These are as follows:

• When a processor is interrupted, it

stops executing its current program and calls a special routine which

"services" the interrupt. The event that causes the interruption is

called interrupt and the special routine which is executed is called interrupt

service routine.

1. The processor completes its current

instruction. No instruction is cut-off in the middle of its execution.

2. The program counter's current

contents are stored on the stack. Remember, during the execution of an

instruction the program counter is pointing to the memory location for the next

instruction.

3. The program counter is loaded with

the address of an interrupt service routine.

4. Program execution continues with the

instruction taken from the memory location pointed by the new program counter

contents.

5. The interrupt program continues to

execute until a return instruction is executed.

6. After execution of from the RET

instruction processor gets the old address (the address of the next instruction

where the interrupt service routine was called.) of the program counter form

the stack and puts it back into the program counter. This allows the

interrupted program to continue executing at the instruction following the one

where it was interrupted. Fig. 8.8.2 shows the response to interrupt with

flowchart and diagram.

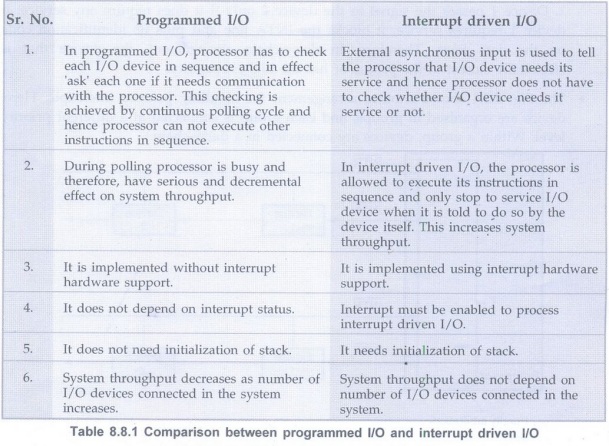

Comparison between Programmed I/O and Interrupt Driven I/O

The Table 8.8.1 gives the comparison

between programmed I/O and interrupt driven I/O.

Interrupt Priority Schemes

•In case polling to identify the

interrupting device, priority is automatically assigned by the order in which

devices are polled. Therefore, no further arrangement is required to

accommodate simultaneous interrupt requests. However, in case of vectored

interrupts, the priority of any device is usually determined by the way the

device is connected to the processor. Most common way to connect the devices is

to form a daisy chain, as shown in the Fig. 8.8.3. As shown in the Fig. 8.8.3,

the interrupt request line ![]() is common to all devices and

the interrupt acknowledge line (INTA) is connected in a daisy-chain fashion. In

daisy-chain fashion the signal is allowed to propagate serially through the

devices. When more than one devices issue an interrupt request, the

is common to all devices and

the interrupt acknowledge line (INTA) is connected in a daisy-chain fashion. In

daisy-chain fashion the signal is allowed to propagate serially through the

devices. When more than one devices issue an interrupt request, the ![]() line

is activated and processor responds by setting the INTA line. This signal is

received by device 1. Device 1 passes the signal to the device 2 only if it

does require any service. If device 1 requires service, it blocks the INTA line

and puts its identification code on the data lines. Therefore, in daisy-chain

arrangement, the device that is electrically closest to the processor has the

highest priority.

line

is activated and processor responds by setting the INTA line. This signal is

received by device 1. Device 1 passes the signal to the device 2 only if it

does require any service. If device 1 requires service, it blocks the INTA line

and puts its identification code on the data lines. Therefore, in daisy-chain

arrangement, the device that is electrically closest to the processor has the

highest priority.

• The Fig. 8.8.4 shows another

arrangement for handling priority interrupts. Here, device are organised in

groups, and each group is connected at a different priority level. Within a

group, devices are connected in a daisy-chain.

Review Questions

1. What is interrupt? AU: Dec.-09, 12,

Marks 2

2. What is the basic difference between

branch instruction a call subroutine instruction and program interrupt?

3. Discuss the general steps involved in interrupt driven data transfer. AU: Dec.-06, Marks 6

4. How does the processor handle an interrupt request ? AU: May-07, Dec.-07, Marks 2

5. Explain the following: Hardware

interrupts. AU Dec.-10, Marks 4

6. Write short note on : Interrupts. AU:

Dec.-08, May-13, Marks 5

7. What are the steps in handling

interrupts ? AU: Dec.-11,18, Marks 6

8. Why are interrupt masks provided in any processor ? AU May-06, Marks 2

9. What is a non-maskable interrupt? What

is the action performed on receipt of a NMI? AU: Dec.-08, Marks 2

10. What are vectored interrupts ? AU:

May-09, Marks 2

11. What do you mean by interrupt

nesting?

12. What is priority interrupt? AU:

May-08, Marks 8

13. Explain the interrupt priority schemes. AU

May-12, Marks 8

14. Explain the different types of

interrupts and the different ways of handling interrupts. AU: Dec.-12, Marks

12

15. Design and explain a parallel priority interrupt hardware for a system with eight interrupt sources. AU: Dec.-16, Marks 15

Digital Principles and Computer Organization: Unit V: Memory and I/O : Tag: : Memory and I/O - Digital Principles and Computer Organization - Interrupt I/O

Related Topics

Related Subjects

Digital Principles and Computer Organization

CS3351 3rd Semester CSE Dept | 2021 Regulation | 3rd Semester CSE Dept 2021 Regulation