Introduction to Operating Systems: Unit III: Memory Management

Demand Paging

Memory Management - Introduction to Operating Systems

In demand paging, a page is loaded into primary memory only when the process references it. It is the simplest fetch policy implemented in virtual memory.

Demand Paging

• In

demand paging, a page is loaded into primary memory only when the process

references it. It is the simplest fetch policy implemented in virtual memory.

Fig. 4.10.1 shows concept of demand paging.

• Demand paging guarantees that the

system brings into primary memory only those pages that processes actually

need. It involves interaction between hardware and software component of the

virtual memory.

• Paging with swapping method will

become as demand paging concept. Process's logical address space is stored on

the secondary storage device.

•

Demand paging requires that the page map table for each process keep track of

each page as it is loaded or removed from primary memory..

• When user want to execute a process,

user swap a process into a memory. Lazy swapper is used for swapping the

process into memory. Lazy swapper swaps the pages whenever needed.

Working

of demand paging

1. Program attempts to find a page.

2.

If the page is located in the primary memory, then the program executes.

3.

If the page cannot be found in the primary memory, then the page fault occurs.

4.

Memory reference is checked for required page to determine it is a valid

reference to a location on a secondary storage, if it is then the page will be

required page. If not, the process is terminated.

5. Schedule disk operation to read the

required page into primary memory.

6. Restart the instruction that was

interrupted by the OS trap.

•

Demand paging takes support from hardware to distinguish the pages. The

valid-invalid bit method is used. This method gives the idea about page

location. Page may be in the primary memory or in the secondary storage.

•

If valid bit is set, then required page is stored in the primary memory. When

an invalid bit is set, then page is on the secondary storage disk.

•

Valid-invalid bit field is attached with page table. Fig. 4.10.2 shows page

table entry.

• The valid-invalid bit field contain a

boolean value to indicate whether the page exists in primary memory.

0 = Not in memory

1 = In memory

•

Initially all valid-invalid entries are set to 0. This information is used for

replacement algorithm. Page fault leads to the page replacement operation to

load the required pages in primary memory.

A

failure to find a page in memory is often called a page fault.

Demand

paging is most efficient when users are aware of the page size used by

operating system.

Steps in Handling a Page Fault

Fig.

4.10.3 shows page fault handling steps in demand paging.

When

page fault occurs, the system performs following steps:

1. Check the process control block table

for reference which bit is set i.e. valid bit or invalid bit for memory access.

2. If invalid bit is set, user will

terminate the process. If valid bit is set, then the page is loaded into

memory.

3. Check for

free frame for new page loading.

4.

Start reading secondary storage device for desired page for allocated frame.

5.

Required page is loaded into the memory after completion of read operation. PCB

table is updated.

6. System restart the instruction that

was interrupted by the error. Page is loaded in memory so process can use it.

Demand Paging Performance

•

Demand paging is a solution to inefficient memory utilization. Performance of

the computer system is affected by demand paging. Effective access time for a

demand paged memory is calculated as follows:

• Since demand paging like caching, can

compute average access time. Memory access time (m) for most computers now

ranges from 10 to 200 nanoseconds. If there is no page fault, then

Effective

access time = Memory access time

• If there is page fault, then

Effective access time = Hit rate x Hit

time + Miss rate x Miss time

=

Hit time + Miss rate x Miss penalty

Effective access time = Memory access time * (1-p) +p* page

fault service time

where

p is the probability of a page fault

• Effective access time is directly

proportional to page fault rate.

• Suppose memory access time = 100 ns,

Page fault service time = 25 ms then Effective access time = Memory access time

* (1 - p) + p * page fault service time = 100 (1 - p) + p * 25,000,000

=

100+ 24,999,900 p

Advantages of Demand Paging

1. Large virtual memory.

2.

More efficient use of memory.

3. Unconstrained multiprogramming. There

is no limit on degree of multiprogramming.

Disadvantages of Demand Paging

1. Number of tables and amount of

processor over head for handling page interrupts are greater than in the case

of the simple paged management techniques.

2. Due to the lack of an explicit

constraints on a jobs address space size.

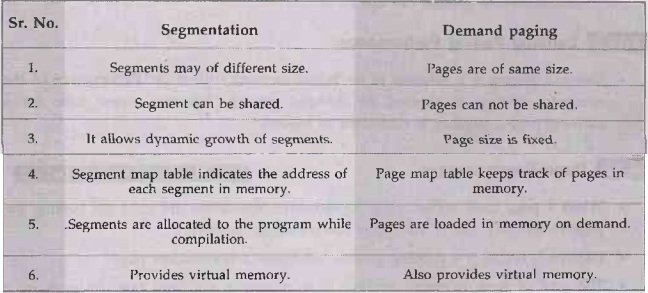

Comparison of Demand Paging with Segmentation

Introduction to Operating Systems: Unit III: Memory Management : Tag: : Memory Management - Introduction to Operating Systems - Demand Paging

Related Topics

Related Subjects

Introduction to Operating Systems

CS3451 4th Semester CSE Dept | 2021 Regulation | 4th Semester CSE Dept 2021 Regulation